|

|

[ Marcony @ 28.09.2019. 13:39 ] @

|

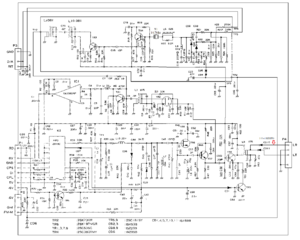

| Pokusavam popraviti jedan uredjaj, kojem je neispravan PLL deo.

Moze li neko objasniti ovu semu, npr. naponski nivoi i frekvencija na odredjenim tackama, kako bih utvrdio gde je tacno problem na ovoj plocici?

Ono sto znam (iz uputstva za uredjaj) je da bi na TP1 napon trebao biti oko 3V @145MHz.

Takodje, TP6 je na max 1V.

|

[ RoRa @ 28.09.2019. 19:49 ] @

"Srce" ovoga elektronskog kola PLL sintetizatora za 2M opseg je IC uPD2819C, PLL sintetizator. Nađite na netu DS ovoga IC i videćete da kolo, srećom, ima dosta kontrolnih (pinova) izvoda. Merenja na ovim pinovima mogu uputiti na mesto problema.

Sintetizator je izveden sa ofset oscilatorom, TR4 na približno 14.7 MHz, i mešačem, Tr1, tako da na PLL kolo (uPD2819C) dolazi razlika izlazne trekvencije 144-146 MHz i (verovatno) 9-tog harmonika ofset oscilatora.

[ Marcony @ 28.09.2019. 22:25 ] @

Citao sam vec o ovom kolu. Ono sto sam do sada utvrdio je da kristal na 5.76MHz radi, kao i onaj u oscilatoru od 14.7MHz (izmereno frekvencmetrom).

Medjutim, nemam odgovarajucu sondu za vise frekvencije, pa ne mogu tacno proveriti sta izlazi na tacki TP2.

Ako sam dobro razumeo, tu bi trebalo biti oko 14.7*9 = oko 132MHz?

+5V, +8V i -6V naponski nivoi su u redu.

D/A iz CPU-a salje odgovarajuce naponske nivoe ofset oscilatoru (TP6).

Tacka TP1 bi po pravilu trebala biti na 3-4V, medjutim, voltmetar tu ne pokazuje nista, cak i promenom kapaciteta CV1.

Ono kako sam razumeo ovo kolo (uPD2819C) je sledece:

- referentni signal je 5.76MHz

- signal za komparaciju stize na pin 14 (iz TA7060AP)

- ako postoji neka razlika, menja se izlazni napon na pinu 8, sto dalje utice na varikap diodu CD8, a ujedno i ukljucuje oscilatorni deo TR6,7 i 8.

- preko C12 i TR2 se signal vraca nazad, na "proveru"

Ispravite me ako gresim.

Inace - preporuka za sondu za frekvencmetar do 500MHz, 50oma/5V max?

[ TRUE RMS @ 28.09.2019. 22:58 ] @

Marcony,

šaljem ti sondu koja može više od 300MHz-a, na kučnu adresu,

ako je u pitanju BNC priključak.

(Sve je "KostenLos", kad završiš, vratiš, mesec, dva, 3, 6, nebitno)

Ako se slažeš javi se na PP.

Ako ne želiš, nikom ništa.

Poz

[ RoRa @ 29.09.2019. 19:07 ] @

PLL kolo u faznom detektoru, izlaz na pinu 8, vrši upoređivanje signala referentne frekvencije ( izlaz iz delitelja ref. frekvencije) sa signalom na izlazu iz programabilnog delitelja.

Ulazni signal ref. delitelja ima frekvenciju od 5.76 MHz. Signal na ulazu u programabilni delitelj ima frekvenciju jednaku razlici frekvencija izlaza PLL sintetizatora i nekog harmonika ofset oscilatora.

Signal ref. frekvencije, prisutan na pinu 9, je 10, 9, 5, 4.5, 2.5 ili 1 KHz u zavisnosti kako je programiran ref. delitelj.

Signal na izlazu programabilnog delitelja, prisutan na pinu 10, mora imati frekvenciju jednaku referentnoj frekvenciji.

Ako ove dve frekvencije nisu jednake onda se na pinu 7 pojavljuje signal koji gasi signal na izlazu PLL sintetizatora.

Dakle, proverite signale na pinovima 9 i 10.

Napomena: kolo PLL sintetizatora je svojevrsni regulator faze VCO-a pa greška na nekom mestu ima za posledicu da su u kolu SVI signali "pogrešni".

Problem se rešava prekidom u ovom zatvorenom kolu, ali o tome kasnije.

[ Marcony @ 23.10.2019. 07:49 ] @

Simptomi su sledeci:

- ukljucim uredjaj, na izlazu modula (CD10 na semi) odgovarajuca frekvencija (133.300MHz).

- posle nepunih 30-ak sekundi izlazna frekvencija postaje nestabilna (varira od 0 do 133MHz)

- minut dva kasnije - 0MHz

- nakon (otprilike) sat vremena rada (nista ne diram, ne merim, ne pomeram), na izlazu modula pojavljuje se stabilna frekvencija koja kao takva ostaje dok se uredjaj ne iskljuci.

PLL IC:

Pin 2 - 5.76MHz (sve vreme)

Pin 9 - 10KHz (sve vreme)

Pin 10 - kada je sve ispravno - 10KHz, kada modul ne radi kako treba - oko 3KHz

Svi elektroliti na modulu zamenjeni (svi osim C42 (0.1uF) - nisam imao pri ruci).

Frekvencmetrom ne mogu nista detektovati na C7 (cak ni kada je sve u redu), pa samim tim ne mogu znati da li je osnovni oscilator ispravan u trenutku kada na izlazu iz PLL modula nema odgovarajuce frekvencije.

[ RoRa @ 24.10.2019. 09:47 ] @

Za nastavak dijagnostike potrebno je raskinuti dva kola zatvorene petlje.

1. između voda +5V i baze tranzistora TR9 spojiti otpornik 100k. Ovim se sprečava gašenje VCO-a signalom sa IC PLL.

2. na TP1 dovesti "tvrd" napon približno jednak početnom naponu (dok sintetizator radi ispravno) na istom TP1. Ovo se može uraditi spajanjem na TP1 klizača potenciometra od 1K, krajevi potenciometra spojeni za +5V i masu.

Frekvencmetrom meriti frekvenciju signala na kondenzatoru C1, ulazni signal u programabilni delitelj IC PLL.

[ Marcony @ 26.10.2019. 12:43 ] @

Epilog - digitalni deo koji upravlja celim uredjajem je imao hladne lemove koje sam prelemio. Sada je i PLL modul ispravan.

RoRa, hvala na podrsci i savetima.

[ Marcony @ 27.10.2019. 09:08 ] @

Dok sam pokusavao da resim problem PLL modula, gledao sam i drugacije varijante - Si5351B.

Da li postoje odredjeni problemi koje treba imati na umu (npr. oblik izlaznog signala, filtriranje...) ako bi se postojeci PLL modul zamenio ovim kolom?

Copyright (C) 2001-2024 by www.elitesecurity.org. All rights reserved.

|