[ aleksazr @ 10.09.2012. 17:37 ] @

| Da ne pišem sad na srpskom... ka zna Altium dobro? http://www.edaboard.com/thread265286.html |

|

[ aleksazr @ 10.09.2012. 17:37 ] @

[ bogdan.kecman @ 10.09.2012. 18:50 ] @

odlicno mesto da postavis to pitanje:

http://www.eevblog.com/forum/altium-designer/ dave je radio u altiumu + ima tamo brdo ljudi koji trose altium ... (ja ga ne znam dovoljno da odgovorim na tvoje pitanje ali kapiram da ces tamo dobiti odgovor isti dan) [ aleksazr @ 10.09.2012. 18:57 ] @

Hvala puno na linku

[ foxhunter1 @ 11.09.2012. 13:26 ] @

Citat: aleksazr: Da ne pišem sad na srpskom... ka zna Altium dobro? http://www.edaboard.com/thread265286.html Ovo sto tebi treba je 'Net Tie' . Brza pretraga na Googlu 'altium net tie' i prvi link je bas ono sto tebi treba: Link za PDF dokument [ aleksazr @ 11.09.2012. 20:41 ] @

Sad sam umoran da probam... koliko vidim, potrebno je baš postaviti komponentu u PCB?

Ne znam da li takva komponenta već ima u library ili mora da se napravi? I koja je minimalna veličina te komponente? Jer lepo je staviti to kao jasnu vezu između dva grounda, recimo, ali negde imam baš puno spojeva između 3V3 i raznih vodova za CPU, FPGA, memorije... gde sam u šemi nacrtao da svaki ima svoj net, iako svi koriste isti napon. Inače, rešio sam to, ali nisam baš oduševljen - link. [ bogdan.kecman @ 11.09.2012. 21:09 ] @

Citat: aleksazr: ali negde imam baš puno spojeva između 3V3 i raznih vodova za CPU, FPGA, memorije... gde sam u šemi nacrtao da svaki ima svoj net, iako svi koriste isti napon. To nema nikakvog smisla? Zasto bi to radio? Jedno je ako imas analogni gnd i digitalni gnd pa hoces da ih spojis u jednoj tacki kako je pravilno, ili ako imas odvojeni deo kola, npr dcdc kontroler, pa hoces da odvojis signale u dcdc kolu od signala (ground posebno) u ostalom delu kola.... ali da imas 20 Vcc-ova zasebno bez ikakvog razloga (kao sto si ti napravio), to nema nikakavog smisla?! Sta si probao da dobijes takvim nazivom net-a? Mozda to moze da se uradi drugacije... [ aleksazr @ 11.09.2012. 21:40 ] @

Zbog preglednosti.

CPU ima VDD za I/O i za analog, memorija za I/O i interni rad, FPGA za I/O i AUX... dakle bar 6 grana za 3V3. Kad im dam posebne netove, lakše se vidi gde koja grana ide... gde ću staviti veći rasprežni kondezator. Ne sećam se da li sam to pročitao negde ili sam tako krenuo jer je tako označeno na tim čipovima. Doduše, tih 6 grana se svedu na 3 jer imam samo dva layera :( Ostali, sitniji čipovi, njih samo vežem na 3V3. [ bogdan.kecman @ 12.09.2012. 09:22 ] @

ja ne vidim tu neki smisao, ok je kada su to stvarno razliciti railovi, ali kada pricamo o istom rail-u nema tu nista preglednije ... no .. kako god ..

[ mradomir @ 12.09.2012. 17:02 ] @

Nacrtaj tako kako si počeo, pa na kraju:

Design -> Netlist -> Clean All Nets Trebalo bi da ti izbriše višak konekcija. Citat: bogdan.kecman: ja ne vidim tu neki smisao, ok je kada su to stvarno razliciti railovi, ali kada pricamo o istom rail-u nema tu nista preglednije ... no .. kako god .. Mislim da Aleksa govori o preglednosti prilikom rutiranja - dizajniranja PCB-a, a ispravno razmišlja kada odvaja, recimo, napajanje analognog i digitalnog dela. Za tim u većini slučajeva nema potrebe, ali ako u datasheet-u tako piše... [ bogdan.kecman @ 12.09.2012. 17:24 ] @

ne slazem se da je preglednija ako to ne koristis. Ako ces da rutiras segmente odvojeno i onda da ih spajas u jednoj tacki (kao sto treba za agnd+gnd) onda ti spajanje neta kako je kolega pokazao i linkovao pdf radi 1/1, ako ces da ih zoves drugacije a onda da ih rutiras kao jedan net onda je to cisto gubljenje vremena i cak naprotiv - smanjuje preglednost … u svakom slucaju to je moje misljenje

[ mradomir @ 12.09.2012. 18:18 ] @

Nismo se baš nešto razumeli, i ja mislim da nije preglednije, ali i nisam nikada crtao matičnu ploču za Pc, jel'.

Očigledno je Net tie način na koji se to radi. Aleksa, da bi kondenzatore (i ostalu boraniju) smestio pored komponenti gde im je mesto, evo šta ja radim: u shematic-u postaviš kondenzator pored komponente kojoj pripada, a ne na gomilu, kako neki vole. Selektuješ grupu komponenti u nekom sklopu - celini, koje hoćeš da rasporediš na PCB. Klikneš Tools -> Select PCB components. Prebaciće te u PCB editor sa selektovanim komponentama iz shematic-a. Dalje: Tools -> Interactive Placement -> Arrange within rectangle. Selektuješ neku praznu površinu pored PCB-a. Altium će ti unutar te površine rasporediti komponente koje si prethodno selektovao u shematic-u. Dalje ih postavljaš kako hoćeš. [ bogdan.kecman @ 12.09.2012. 18:54 ] @

net tie je keva, bas mi krivo sto nisam znao za njega, ja sam to budzio .. nebitno .. blam me :D

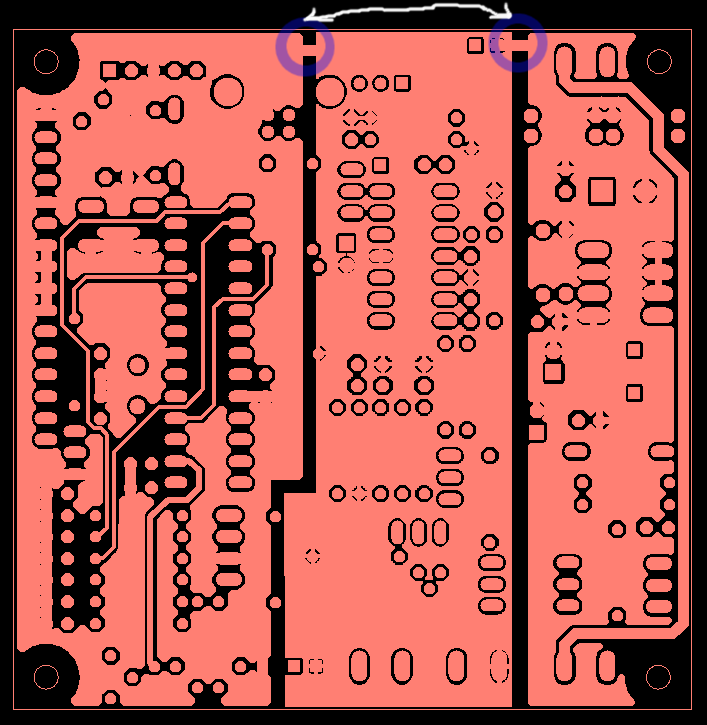

koji god jaci mcu, cpu ili fpga da stavis imas brdo pinova za napajanje, sto istih sto razlicitih .. i imas brdo komponenti koje moraju da budu "tu blizu" - tu je mogucnost altiuma da komponente koje odaberes u schematic delu selektuje u pcb delu i uradi interactive placement keva posto tako nesto u gomili drugih eda alata mozes samo da sanjas ... ja dosta plocki pravim sa fpga i sa armovima i mnogo napajanja i mnogo razlicitih i istih groundova je skroz normalna pojava ali koliko sam ja ovde shvatio on ima 3v3 na mcu-u koji je isti net (fizicki i logicki) kao 3v3 na i2c port extenderu i spi senzoru za coolness ali je sva 3 net-a nazvao razlicito "da bi mu bilo preglednije" a onda kad ih rutira mu je nezgodno da stavlja net tie posto jeli rutira sve na isto jerbo na samom pcb-u to je logicno jedan vod i nema nikakvog smisla budziti "spajanje netova u jednoj tacki" kad je to prosto sve obican 3v3. kada imas ovako nesto (crtao jedan kolega ovde sa foruma), onda ima svrhe da razdvajas, ili ako radis analog/digital .. ali da razdvajas "negde imam baš puno spojeva između 3V3 i raznih vodova za CPU, FPGA, memorije... gde sam u šemi nacrtao da svaki ima svoj net, iako svi koriste isti napon." koje ce sve da idu sa istog LDO-a ne pravi preglednost vec potpuno suprotan efekat  [ aleksazr @ 12.09.2012. 21:44 ] @

@mradomir

Slično i ja radim, ali samo jednom odaberem Tools, Cross Select Mode i onda selektujem komponentu u SCH i prebacim se u PCB i tamo je isto selektovana. Isto ima i u PCB meniju Cross Select Mode. Obično otvorim samo tu šemu gde su delovi koje postavljam pa sa Ctrl+TAB skačem u PCB. Isto radimo i sa kondezatorima. Konkretno, imam 3 vrste kondezatora: 1. Oba pina su hidden i spojena na VCC i GND, samo je grafički nacrtan kondezator. Ovaj postavim pored čipa. 2. GND pin je hidden, a VCC prikazan - kad spajam na 3V3 a ne na standarnih 5V. Ovaj postavim na sam VCC pin čipa. 3. Oba pina prikazana - mogu i masu da menjam. @bogdan Ne, nisam sve netove nazvao drugačije. Imam jedan 3V3 koji koristim za većinu čipova, jer manje troše. SDRAM vuče 200mA pri refreshu i za njega imam poseban net, da lako izrutam granu za njega. Koliko CPU i FPGA vuku za I/O nemam pojma, ali sam isto tako uradio. Slično imam recimo za dva motora na 12V, oba imaju svoj 12V iako imaju isti napon. [ mradomir @ 14.09.2012. 16:37 ] @

Aleksa, ajde pojasni ovo sa kondenzatorima i hidden padovima, nije mi baš jasno čemu to služi, a uz to...

[ bogdan.kecman @ 14.09.2012. 18:15 ] @

za sakrivanje pinova ima mnogo korisnih razloga, posebno za vss... to je super fora koju ima svaki bolji eda alat i smanjuje guzvu u semi... ali mislim da za kondove nema mnogo koristi za ovo, bar po mom misljenju, ja volim da vidim gde je kond vezan ... za neki fpga me bas briga da mu vidim 235 gnd pinova ... ali za kond ocu da vidim de ide ..

dodatno je smor, kako ti se ti kondovi posle prikazuju u BOM-u, da li ce da ti lepo kaze da imas 200 100nF 0603 ili ce da ti kaze da imas 150 ovih 100nF, 20 onih 100nF i 30 onakvih 100nF - a svi isti, samo nekima sakriven ovaj a nekima onaj pin .. [ aleksazr @ 14.09.2012. 22:31 ] @

@mradomir:

K68 ima sakrivena oba pina i pripada U22 čipu. K65 ima sakriven GND pin i pripada U18 čipu. K16 ima prikazana oba pina. Inače, koristim designator K, a ne C, da znam da se radi o rasprežnom kondezatoru. @bogdan: nema problema sa BOM raportom. [ mradomir @ 15.09.2012. 13:11 ] @

@aleksazr

prethodno te nisam razumeo, kontao sam da pričaš o pad-ovima - sada je jasnije (o čemu pričamo), ali mi nije jasno zašto tako crtaš kondenzatore. Mali savet - još neko će da gleda tvoju šemu, meni lično je trebalo malo vremena da shvatim o čemu se tu radi, a trebalo bi da bude očigledno na prvi pogled. Recimo ovako:  [ aleksazr @ 15.09.2012. 14:43 ] @

Pa svako ima svoj stil, kao što ti stavljaš portove svuda :)

[ bogdan.kecman @ 15.09.2012. 18:39 ] @

portovi su najbolja stvar posle rezanog leba :D i extra su pregledni (doduse radomir je ovde malo preterao :D )

kod tebe na clipu ima 10 kockica od toga su nesto kondenzatori, nesto je nesto drugo, treba ti staklena kugla da skontas sta je pisac hteo da kaze .. to nikom osim tebi koji si crtao nije pregledno, a sto je najbolje - nije ni tebi pregledno posle nekog vremena, ti mozda mislis da jeste posto mislis da moras da procitas dal je nesto Kxx ili Zxx ili Dxx da bi znao sta je, ali je 10x brze kada vidis simbol nego kada citas anotaciju i tebi i bilo kome drugom... [ mradomir @ 17.09.2012. 00:54 ] @

Priznajem da preterujem sa portovima al' mi se kasnije projektovanje svodi na ctrl-c, ctrl-v, a i sve je kristalno jasno, čak i posle, mislim petog lava, a sutra je ponedeljak, jeb'ga.

[ bogdan.kecman @ 17.09.2012. 08:17 ] @

ja bi na tvom snipetu GND vezao na GND a ne na port i VCC/AVCC/AREF vezao na VCC/AVCC/AREF umesto na portove .. sve ostalo bi ostavio isto sa portovima i onda isto cc/cv radi posao a po meni izgleda preglednije .. no tu sad vec ulazimo u personalne preference

[ aleksazr @ 17.09.2012. 10:05 ] @

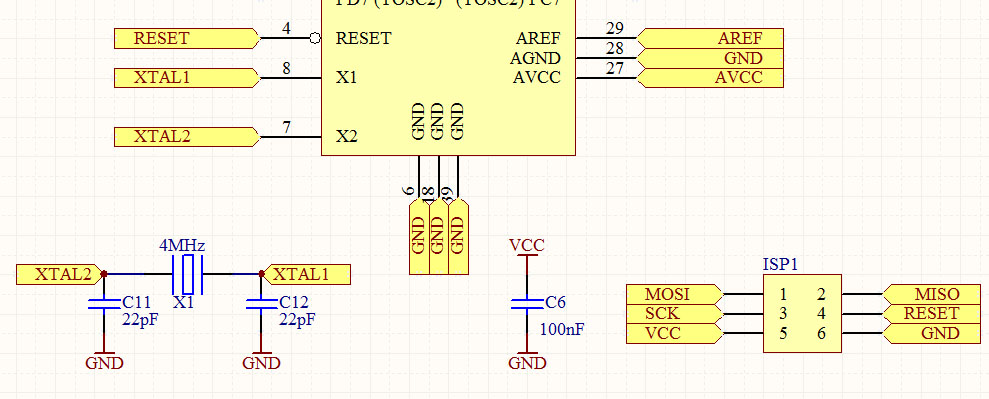

Osnovna namena portova je da prenese signal sa jedne šeme na drugu, a čisto sumnjam da XTAL1 i XTAL dolaze sa druge šeme.

Pa kad govorite da neko drugi neće razumeti šemu - to je savršen primer. Tražiće port na drugim šemama, a nema ga. Nije da Net label nisu čitljivi... a rade i sa copy paste. [ bogdan.kecman @ 17.09.2012. 10:46 ] @

mislis drugi sheet za istu semu ... kad stavis port onda lako prebacujes izmedju sheetova ako ti treba, pravis sub-blokove i slicno .. meni je obican net-name ultra nepregledan ..

[ mradomir @ 19.09.2012. 09:02 ] @

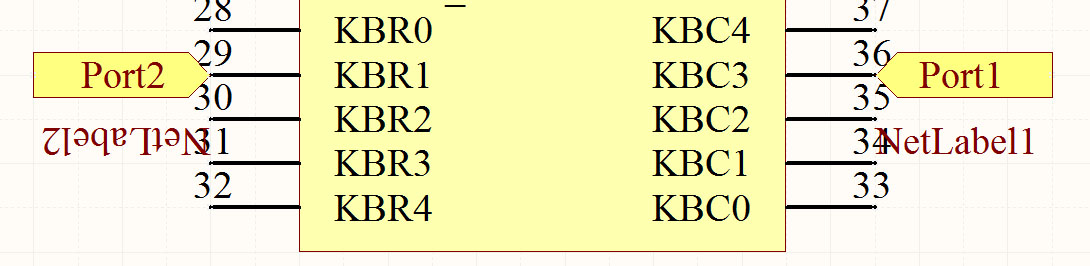

Citat: aleksazr: Osnovna namena portova je da prenese signal sa jedne šeme na drugu, a čisto sumnjam da XTAL1 i XTAL dolaze sa druge šeme. Pa kad govorite da neko drugi neće razumeti šemu - to je savršen primer. Tražiće port na drugim šemama, a nema ga. Nije da Net label nisu čitljivi... a rade i sa copy paste. Jeste osnovna, ali nije i jedina namena, u jednom sheet-u port-ovi funkcionišu bez greške. A što se tiče Net label-a pogledaj ispod pa mi kaži šta je preglednije od ova dva.  Portovi se automatski rotiraju, dok Net label moraš ručno. Pa se preklapaju sa brojevima... Na XTAL stavljam portove, jer često ponestane mesta, pa da ne bi povećavao format sheet-a, lakše je malo ispomerati elemente. Moj savet je, ako je samo jedan sheet u pitanju, mogu portovi. Ako je više sheet-ova, portovi za vezu između sheet-ova, a wire i bus unutar sheet-a. Citat: bogdan.kecman: ja bi na tvom snipetu GND vezao na GND a ne na port i VCC/AVCC/AREF vezao na VCC/AVCC/AREF umesto na portove .. sve ostalo bi ostavio isto sa portovima i onda isto cc/cv radi posao a po meni izgleda preglednije .. no tu sad vec ulazimo u personalne preference Ovo je čisto estetski - lepše mi izgleda kada su svi portovi, pa su kod napajanja povezani "portovi" i "power portovi", ali kako se kome sviđa... [ ZAS011 @ 19.09.2012. 09:38 ] @

E baš si lepo turio te Nel Label-e

Ne meću se na Pin-ove već na "žičke" 'vako:  Pa kaži da nije pregledno [ bogdan.kecman @ 19.09.2012. 11:24 ] @

Citat: ZAS011: E baš si lepo turio te Nel Label-e :( Ne meću se na Pin-ove već na "žičke" Pa kaži da nije pregledno :) Meni su portovi i dalje 100x pregledniji, da ne spominjem da za port mozes da definises el input, output, bidirectional... [ mradomir @ 19.09.2012. 13:24 ] @

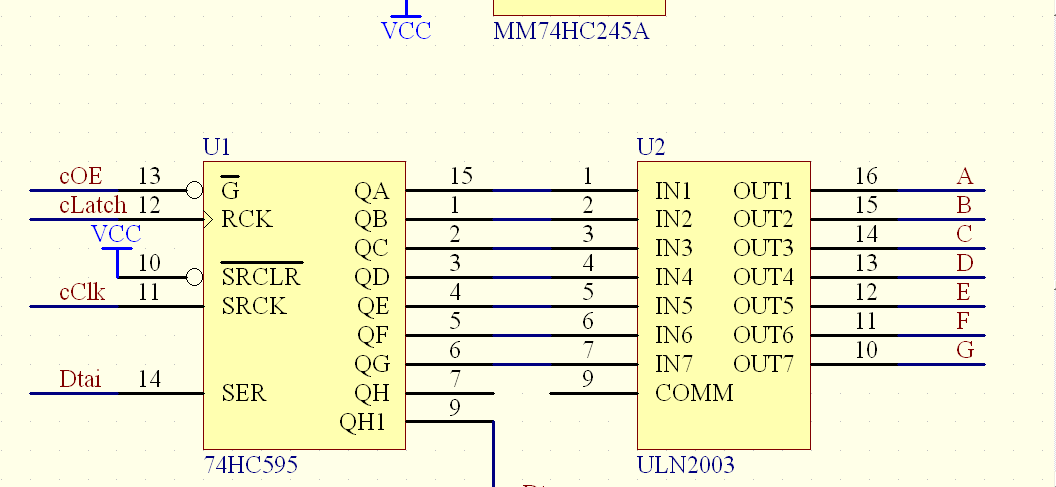

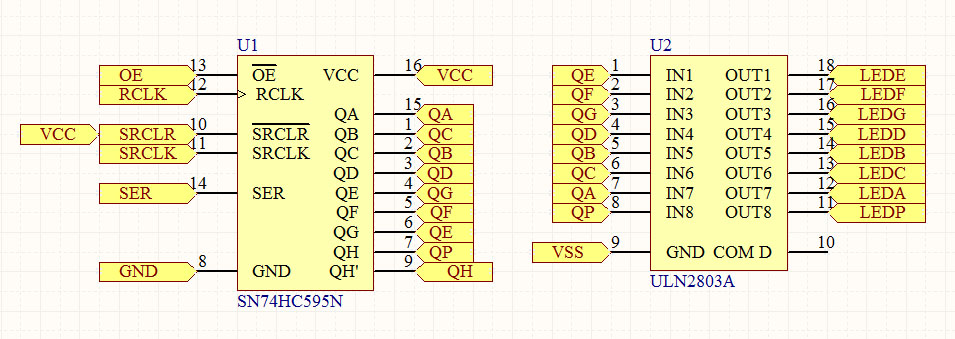

Evo isto to ali lepše :)

Šalim se. Ovo je primer gde bi povezivanje linijama napravilo haos (obratite pažnju na raspored ulaznih signala ULN-a). Meni je tako odgovaralo zbog rutiranja. Mogao sam da stavim i Bus ali treba da ga nacrtam, pa da stavim Bus Entry, pa Wire do pina, pa Net Label - verovatno sam malo lenj. Da skratim raspravu, po PS-u (za one mlađe civile - Pravila Službe), koriste se "Net Label" i "Bus", a za nešto jednostavnije može da prođe i "Port". [ bogdan.kecman @ 19.09.2012. 13:28 ] @

yup, za ovo bi bus bio mnogo lepsi

[ foxhunter1 @ 19.09.2012. 20:41 ] @

[ ZAS011 @ 19.09.2012. 22:14 ] @

+1

Copyright (C) 2001-2025 by www.elitesecurity.org. All rights reserved.

|