|

|

[ DSL @ 22.08.2019. 14:21 ] @

|

| Anpak, pozdrao,

Kreiram neki bafer za vise signala ali koncept mora biti fail safe i brz . Izlaz je logicko AND sva 4 signala iz optokaplera. Imam na raspolaganju 3-5us da propagiram pojavu kroz kolo...

Imam 4 tranzistora u drugom uredjaju koji su u normalnom stanju provodni i ta provodnost se koristi za teranje LE diode u mom optokapleru.

Ukoliko i jedan od ta 4 signala ode na nulu, LE dioda u njegovom kolu ce se ugasiti i treba da se obori kompletan izlaz, po logici AND.

Pitanje: kako ostvariti logicko AND sa optokaplerima i realizovati ovo kolo? Imao sam ideju koja je podrazumevala da se katoda diode jednog vodi na kolektor drugog optokaplera ali to nije failsafe...

U opcijama je trenutno SFH6156-1 ali ni on se nesto nije proslavio brzinom... preporucite i neki brzi... |

[ djoka_l @ 22.08.2019. 14:39 ] @

Treba ti AND kolo sa četiri ulaza.

Na wiki stranici imaš 3 moguće šeme AND kola sa dva ulaza, samo dodaš još dve diode ili još dva tranzistora: https://en.wikipedia.org/wiki/AND_gate

Ili iskoristiš neki integralac, kao što je 74ALS21 (treba ti pola ovog integralca pošto ima 2 x 4-Input AND). Ako su ti nivoi signala odgovarajući... [ DSL @ 22.08.2019. 14:49 ] @

Sa tim AND kolom bih trebalo da teram diodu sledeceg optokaplera (ciji tranzistor treba da preslika onaj tranzistor sa pocetka). Cenim da ovaj ALS nema strujne mogucnosti da tera LED u optokapleru...

Jos neka ideja? (AKo nesto nije jasno iz moje rogobatne price, dobacicu i koju sliku za koji minut...)

[ veselinovic @ 22.08.2019. 14:51 ] @

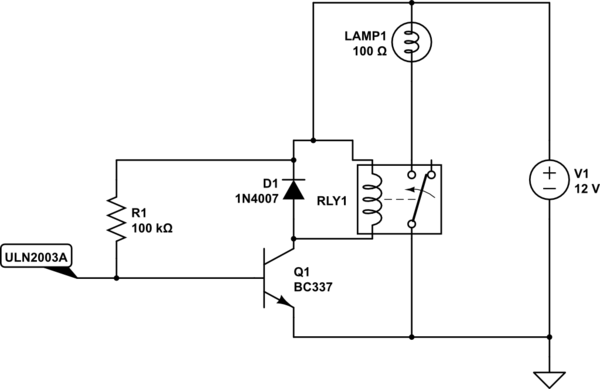

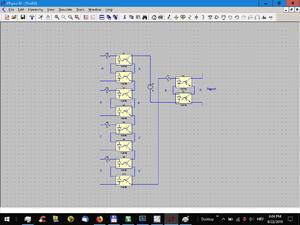

Posto je kod tranzistora sa zajednickim emiterom log nula "jaca" od log 1 dovoljno je napraviti ovakvo kolo.

Tranzistor moze da vozi sta hoces, os relej os opto

[ djoka_l @ 22.08.2019. 14:59 ] @

Jedan tranzistor na izlaz iz ALS?

[ DSL @ 22.08.2019. 15:00 ] @

Jovane i Djoko, pre svega hvala na javljanju...

Ovo je tema koja me svrbi odavno i resio sam je ali su mi danas saopsteni poduslovi i neke izmene pa sve Jovo nanovo...

Jovo, ne znam kako bih primenio ovo tvoje. Ovde imam primarno galvansko odvajanje i fail safe funkciju, ali se dodatno javila brzina propagacije pojave, i to mi veci problem predstavlja gasenje optokaplera jer kudikamo sporije. S druge strane, ne bih da koomplikujem preterano sa dizajnom...jer nemam bas vremena za razvoj..

[ mikikg @ 22.08.2019. 15:14 ] @

Fail-safe logika i "nemam vremena za razvoj" ne idu bas jedno sa drugim :)

Pogledaj ovaj odlican video:

Vital Logic Design / Fail-safe Circuits

https://youtu.be/BeORD7aG3Jc[ DSL @ 22.08.2019. 15:17 ] @

Znam.

Jovo, ukapirao sam sta si mislio. Sutra stavljam ovo na osciloskop i merim propagacije...

Svaki savet u medjuvremenu rado prihvatam..

[Ovu poruku je menjao DSL dana 22.08.2019. u 16:38 GMT+1]

[ macolakg @ 22.08.2019. 16:36 ] @

@DSL,

Koliko sam razumeo iz tvoje priče, tebi treba galvanski razdvojen četvoroulazni AND sa vremenima reakcije ispod 5uS.

Vidim da je počelo neko komplikovano filozofiranje na tu temu. Moj princip visoke pouzdanosti je minimizovati broj komponenti jer sa svakom komponentom raste verovatnoća otkaza.

Sklop koji tebi treba se može krajnje jednostavno napraviti. Vidim da se nešto forsira emiter sekundarnih tranzistora na masi.

Krajevi tranzistora na sekundarnoj strani optokaplera mogu biti bilo gde u granicama probojnosti optokaplera. Jedino se ne smeju prekoračiti specifikacije između emitera i kolektora dotičnog tranzistora.

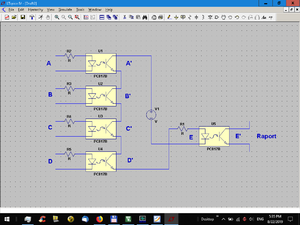

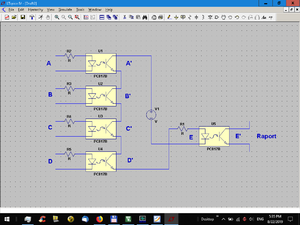

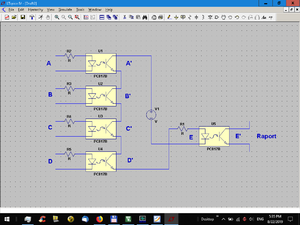

Na primer, sasvim jednostavan i vrlo pouzdan sklop bi izgledao ovako:

Imaš 4 ulazna kola, koja su i međusobno i od ostatka sklopa galvanski razdvojena.

Imaš srednje kolo koje je razdvojeno od ulaza i od raport izlaza i konačno galvanski rastavljen raport izlaz.

Optokapleri tipično propadaju tako što izgube osetljivost (degradacija emisije LED), što ti u ovom slučaju i odgovara jer bilo koji od njih da otkaže ti gubiš izlaz.

Latencija nacrtanih PC817 je tipično 5uS pri 5mA i LED i tranzistora. Dakle ovaj sklop bi kasnio oko 10uS.

No, nikakav problem nije staviti neke drastično brže otpokaplere jer ih ima i do preko 10Mbs...

------------------------------------------------------------

Ono ključno što nisi napisao je očekivan nivo pouzdanosti i uslovi rada sklopa.

Na primer, ako je neophodan više decenijski vek u super teškim uslovima (-55 do +125C) tu optokapleri teško da bi mogli proći.

Onda bi se sklop rešavao nekim induktivnim prenosom ili slično tome...

Pošto pretpostavljam da nije NASA ili Military, onda optokapleri piju vodu.

[Ovu poruku je menjao macolakg dana 22.08.2019. u 17:46 GMT+1]

[Ovu poruku je menjao macolakg dana 22.08.2019. u 17:47 GMT+1][ DSL @ 22.08.2019. 16:55 ] @

Macola, hvala na ucescu.

I moj princip je minimizacija broja komponenti iz istog razloga i zato ne bih da uvodim preterano mnogo komponenti jer je i sam koncept relativno prost.

Problem i jeste vreme propagacije, da ne kazem vreme iskljucivanja sklopa.

Ovo sto si mi predlozio sam imao u glavi (stavise, malo drugacije) ali ulazni signal (da ne kazem, nedostatak istog) je ubio taj moj koncept u startu.

Nažalost, sa onim sto sam imao u momentu igranja na stolu nisam mogao svesti propagaciju na ispod 8us, a i to mi je mnogo...

Daj neki predlog za brzi OC. Koliko vidim, ovi 4 pinski svi idu do 10ak us potrebnih za gasenje a sve brže opcije su neke logic varijante sa 6pinskim kućištima. Nije mi bas grbavo oko velicine OC ali bih da se zadrzim na smd...

(Kad si vec dao ruku...)

Piju OC vodu, pouzdanost je zaista potrebna ali ne radi nista u ovom temp opsegu.

[ macolakg @ 22.08.2019. 16:57 ] @

Drugo pitanje je šta ti to podrazumevaš pod "fail safe"?

- prekid?

- proboj?

Ako hoćeš bezbednost od oba slučaja, onda ti slede dvostruke linije za svaki kanal. Dakle sve dvostruko i na kraju AND kao krunski dokaz.

Srećom, kod korektno dimenzionoisanih struja kroz optokapler (<50% graničnih karakteristika pri datim temperaturnim uslovima), verovatnoća prekida je nekoliko puta veća od verovatnoće proboja, te opet priloženi sklop odgovara.

P.S.

Pošto osiguranje od prekida već imamo, recimo bezbednost od proboja pojedinačne komponente možemo sasvim jednostavno udvostručiti na primer ovako:

[ DSL @ 22.08.2019. 17:06 ] @

Dobro pitanje

Izlaz prethodnog uredjaja je u stvari optokaplerov tranzistor ciji se C i E vode direktno na moj sklop. Ako je sve u redu, taj tranzistor vodi i LED u mom optokapleru veselo sija....

Ukoliko postoji alarm, onaj tranzistor se gasi a moja dioda takodje.

Ukoliko slucajno dodje do kidanja kabla (Fail) moja dioda se opet gasi i to je isto kao da imam alarmno stanje, dakle AND kolo ce odreagovati adekvatno...

[ macolakg @ 22.08.2019. 17:07 ] @

Pogledaj post iznad, pošto sam u međuvremenu pisao.

[ DSL @ 22.08.2019. 17:16 ] @

Mislim da je ovolika fail safe nepotrebna, bitno mi je za sada samo obezbedjenje od kidanja veze.

Druga manjkavost ove varijante bi mi bilo povećanje propagation time-a.

Ovde se radi samo o naponima do 24V, kilovolti su na 10m dalje...

[ macolakg @ 22.08.2019. 17:18 ] @

Citat:

Daj neki predlog za brzi OC. Koliko vidim, ovi 4 pinski svi idu do 10ak us potrebnih za gasenje a sve brže opcije su neke logic varijante sa 6pinskim kućištima. Nije mi bas grbavo oko velicine OC ali bih da se zadrzim na smd...

(Kad si vec dao ruku...)

E sad baš mnogo hoćeš. Premalo je dovoljno brzih sa 4 pina, ali u smd obliku ima brzih sa 6 pinova koliko hoćeš:

Npr:

https://eu.mouser.com/Optoelec...rs/_/N-6zsftZ1yzvvqx?P=1z0yqyd

Naravno ima i mnogo bržih, samo potraži. [ macolakg @ 22.08.2019. 17:25 ] @

Latencija jednog optokaplera je njegova tipična osobina prema vrsti.

PC817 ili LTV817 ima oba vremena reda 5uS. Dakle svaki sledeći u nizu će uneti to kašnjenje.

Onaj sklop koji sam nacrtao (i prva i druga verzija) imaju tipičnu latenciju 10uS.

Ne moraš koristiti optokaplere. Možeš koristiti druge galvanske rastavljače (kapacitativne, induktivne).

Ima ih i sa brzinama koje podržavaju USB 2.0 bez ikakvog problema i sa naponskim marginama koje su ravne marginama optokaplera, takođe i sa dU/dt ravnim ili boljim nego kod optokaplera.

Na primer:

https://eu.mouser.com/Semicond...galvanic+isolators&FS=True

[ DSL @ 22.08.2019. 17:26 ] @

Hehe, daj jos po litre :-)

Hvala ti puno i za ova razmišljanja, ne mora bas na 4 pina,

[ Proza_1 @ 23.08.2019. 00:51 ] @

Naleteo sam na Vishay AN u kojem predlažu za povećanje

brzine standarnih OC koristiti spoj baza-colektor foto-trans.

"Faster Switching from Standard Couplers"

Možda ti da neku ideju.

[ mikikg @ 23.08.2019. 01:08 ] @

Si8233 ima tipican propagacioni delay od 30ns sa izolacijom do 5kV, u cemu je problem? :)

6N137 50ns ...

TLP250 150ns ...

ADuM110N 8.7ns i tako dalje :)

[ DSL @ 23.08.2019. 06:43 ] @

Nema nekih specijalnih problema. Pokusavam da minimizujem i uprostim resenje. U tvom slucaju uvodim i dodatno izolovana napajanja. Videcemo sta kaze ceprkanje po radnom stolu...

Kod standardne ponude optokaplera vreme iskljucenja je za red velicine vece od vremena ukljucenja, a upravo mi je bitno da iz superzasicenog stanja izlazni tranzistor brzo ode u neprovodno. Stvar je igranke u kolu tranzistora da li cemo ga drzati na ivici... Brzina diode ne igra neku specijalnu ulogu, bar sa ovim latencijama o kojima ja pricam, reda us...

Proza_1, interesantna AN. Dosta ukazuje gde treba da (ne) gledam...

[ DSL @ 26.08.2019. 08:37 ] @

Citat: macolakg:

Na primer, sasvim jednostavan i vrlo pouzdan sklop bi izgledao ovako:

Imaš 4 ulazna kola, koja su i međusobno i od ostatka sklopa galvanski razdvojena.

Imaš srednje kolo koje je razdvojeno od ulaza i od raport izlaza i konačno galvanski rastavljeno

Ne mogu da dodjem do interne blok seme ovog Vishay čipa ali cenim da ova kaskadna veza 4 OC pri upotrebi ovog smitovanog optokaplera ne bi bila moguca jer je emiter verovatno klampovan na masu...

https://eu.mouser.com/Optoelec...rs/_/N-6zsftZ1yzvvqx?P=1z0yqyd[ macolakg @ 26.08.2019. 10:36 ] @

@DSL,

Ne možeš upotrebiti te OC jer oni imaju logički sklop umesto opto-tranzistora. Taj logički sklop zahteva sopstveno napajanje po svakom komadu OC. Tu je serijska veza poput one na slici više para nego muzike jer bi ti trebalo 4 lebdeća napajanja.

Za onu vezu kao sa slike možeš upotrebiti isključivo OC sa optotranzistorom na izlazu, sa izvodom baze ili bez njega (4 ili 6 pinova), mosfet ili BJT.

Naravno one koji imaju prihvatljivu brzinu za tvoj slučaj.

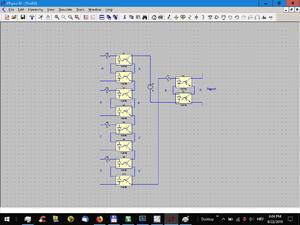

Pošto vidim da se problematično snalaziš sa tim stvarima, evo ti rešenja koje je finalno, samo ćeš se malo poigrati sa par veličina, jer nemam vremena da se tim bavim umesto tebe.

Upotrebićeš Tošibin TLP109, koji je u SO-6 kućištu, čim zadovoljava tvoje potrebe za kompresijom prostora.

Ujedno, taj OC bez posebnih problema postiže prenos reda 200+KHz, te i po drugim parametrima zadovoljava ono što želiš.

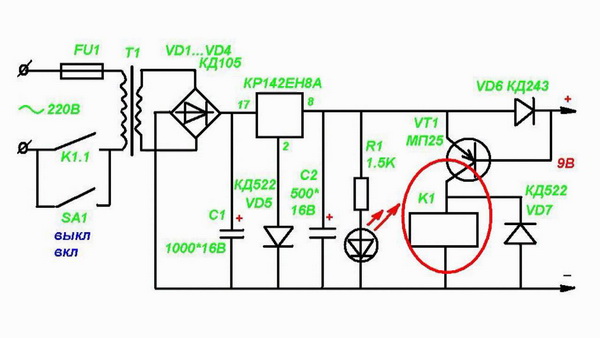

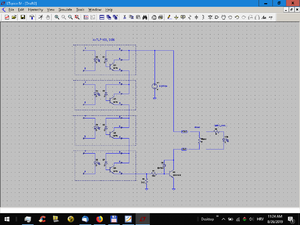

Evo prvo šeme pa ćemo o korekcijama:

Za početak:

- brzina OC raste sa jačinom struje LED, ali takođe i discipacija, a radni vek opada,

- brzina OC raste i sa strujom izlaznog tranzistora,

- brzina OC raste sa smanjenjem otpora opterećenja, ali raste i discipacija kao i šansa da prekoračiš maximum ratings...

Sklop sa slike ima spojenu fotodiodu sa kolektorom optotranzistora. Četiri takva su serijski vezana, i sa JEDNAKIM strujama njihovih LED, dovoljno ravnopravno će podeliti napon napajanja izvora V1 koji može biti u rasponu od 5 do 24Vdc.

Otpornik R2 je ključno opterećenje OC i od njegove veličine zavisi brzina sklopa. Smanjenjem vrednosti tog otpornika ti raste brzina sklopa, ali takođe i rizik da prekoračiš maximum ratings OC.

Drugi deo sklopa je strujni pojačavač sa Baker klampom (D9) koji neuporedivo ubrzava uzlaznu ivicu na kolektoru tranzitora Q5 (odnosno silaznu ako posmatraš struju kao signal).

Ono što tebe zanima je STRUJA kroz R2. Ta struja ne sme preći deklarisanih 8mA, a zavisi (raste) od struje LED i od smanjenja veličine R2, kao i od napona V1.

Veličinu R2 i R1 treba udesiti da pri radnoj struji LED (koju imaš tamo negde na sklopu), ne prekoračiš 8mA kroz sekundarne srane svih OC.

Imaš dve tačke za manipulaciju brzinom i maksimalnom strujom OC: veličine R2 i R1 i napon V1.

Opterećenje sa kog ćeš finalno čitati AND svih OC, može biti neki Rload, kao sa slike, ili neki OC iza.

AND rezultat je STRUJA kolektora Q5, pri čemu će normalno biti invertovano naponsko stanje na njegovom kolektoru.

Ako ti treba nešto drugačije, ili pak neki lebdeći izlaz, onda možeš taj izlaz upotrebiti kao napajanje primarne strane nekog OC (opet TLP109) ili kao bržu opciju direktno iskoristiti izlaz sa Q5.

Dakle, stoji ti da postaviš neki merni otpornik (reda 100R) serijski sa poslednjim emiterom i da na njega zakačiš DVM kao kontrolnik struje koja ne treba preći 8mA SA VRUĆIM OC na bar 80C i sa datom strujom njihovih LED, pri izabranom naponu V1.

Prvo namestiš taj granični parametar, sa trajno uključenim LED na sva 4 OC.

Potom osciloskop na R2 i tu će ti biti dovoljna amplituda reda 2-3Vpk, da ti uredno radi Q5.

R1 za bazu možeš slobodno povećati na 4k7 da ne misliš o toj grani opterećenja, a R2 takođe počni od 4K7 pa na dole.

E onda već seckaj struje LED da proveriš brzinu sklopa i ako je zadovoljavajuća, onda se potrudi da smanjiš struje LED i napon V1 do granice koja zadovoljava brzinu, sa HLADNIM OC na min. temperaturi koju očekuješ u eksploataciji.

I to je to druže.

Pozdrav,

Macola

[Ovu poruku je menjao macolakg dana 26.08.2019. u 12:08 GMT+1]

[Ovu poruku je menjao macolakg dana 26.08.2019. u 12:13 GMT+1][ Living Light @ 26.08.2019. 10:47 ] @

Ovo je tipičan dokaz,

-Kako ljudi ne čitaju ono što im se savetuje.

Pre 3 dana +17 sati ti je macola napisao:

Citat: macolakg: Krajevi tranzistora na sekundarnoj strani optokaplera MOGU BITI BILO GDE U GRANICAMA PROBOJNOSTI OPTOKAPLERA. Jedino se ne smeju prekoračiti specifikacije između emitera i kolektora dotičnog tranzistora.

Znači može C-E da bude i na MARSU, a ulaz OC na ZEMLJI!

Samo ne sme da se prekorači, bla,bla,bla.

Ovo je DIREKTAN odgovor na tvoje pitanje postavljeno pre 2 sata.

I zaboravi "Klampovanje emitera na masu".

Nema tu "mase".

Emiteri mogu da budu bilo gde, i na Jupiteru, jer je sekundar (izlaz OC-a) lebdeći.

Edita: Preduhitrio me macola sa odgovorom.

[ DSL @ 26.08.2019. 10:52 ] @

Hvala na pruzenoj ruci :)

Hoćeš da kažeš da i kod ovog TLP izlazni tranzistor sa C i E sve vreme floatira u odnosu na ostale pinove?

Ne znam zašto ali me sve vreme zbunjuje pin imenovan sa GND a ne sa E... rek’o, ako je ovaj interno spojen negde u kolo, onda ona AND kaskada opet neće funkcionisati...

Već sam ja precesljao ovaj TLP ali videh ovo GND i rek’o...caos...

[ DSL @ 26.08.2019. 10:58 ] @

Citat: Living Light:

Ovo je tipičan dokaz,

-Kako ljudi ne čitaju ono što im se savetuje.

Pre 3 dana +17 sati ti je macola napisao:

Citat: macolakg: Krajevi tranzistora na sekundarnoj strani optokaplera MOGU BITI BILO GDE U GRANICAMA PROBOJNOSTI OPTOKAPLERA. Jedino se ne smeju prekoračiti specifikacije između emitera i kolektora dotičnog tranzistora.

Znači može C-E da bude i na MARSU, a ulaz OC na ZEMLJI!

Samo ne sme da se prekorači, bla,bla,bla.

Ovo je DIREKTAN odgovor na tvoje pitanje postavljeno pre 2 sata.

Edita: Preduhitrio me macola sa odgovorom.

Mislim da ovo nije uopšte odgovor. Nije stvar ovde u naponima između ulaznih i izlaznih delova optokaplera nego činjenice da se u predlozenoj supertotempole konf emiter jednog vezuje za kolektor sledećeg. Ako su emiteri interno klampovani, zakovani za mase onda bi čitava konf izgubila smisao jer bi svi kolektori i emiteri bili na jednom potencijalu... [ Living Light @ 26.08.2019. 11:02 ] @

DSL,

Nemoj da komplikuješ.

Upravo tako, izlaz OC "floatira" u odnosu na "sve živo i ne-živo",

možeš da ih vezuješ bilo gde.

Ajde ovako.

Zamisli da je izlaz OC-a, relejni kontakt, koji je odvojen od špulne, za jedno 5-10kV.

I vozi Miško...

[ Living Light @ 26.08.2019. 11:06 ] @

Šta pričaš?

Kako su emiteri interno klampovani?

-kada su emiteri u razdvojenim kučištima!

Svaki emiter lebdi za sebe, možeš slobodno da ga vežeš za kolektor drugog OC-a.

Veži tako kako je macola rekao, ČUTI i probaj!

TO pije vodu garant.

[ branko tod @ 26.08.2019. 11:14 ] @

DSL, mislim da u quad kućištu nisu povezani emitori međusobno.

To bi bilo glupo jer je takvo kućište odrađeno da mi se ustvari ubrzalo

sklapanje. Uostalom, evo šta piše o tome: The ILD1/2/5 has two isolated

channels in a single DIP package and the ILQ1/2/5 has four isolated channels

per package.

Roberte, čovek priča o quad optokapleru.

[ macolakg @ 26.08.2019. 11:19 ] @

Roberte,

Oni OC sa šmitom su digitalitovani unutra i moraju imati fiksno napajanje na pinovima 6 i 4. Onda njihov izlaz (5) radi u odnosu na na pin 4.

Ta verzija poseduje kompleksan sklop unutra i ne može se vezivati onako serijski kao što mu je bilo nacrtano.

Kao što sam i napomenuo, moraju OC koji imaju "čisto" stanje unutra, poput fotodiode sa BJT iza ili foto tranzistora.

Pronašao sam mu TLP109 koji će pokriti sve što mu treba (post iznad).

[ Living Light @ 26.08.2019. 11:19 ] @

[ macolakg @ 26.08.2019. 11:20 ] @

Ne treba njemu quad OC jer mu je dojava razbacana.

[ macolakg @ 26.08.2019. 11:32 ] @

Van toga, na četvorostrukom OC je varnična distanca između kanala drastično manja nego primar-sekundar i o tome treba voditi računa kod primene.

Smatrajte stvar rešenom i bespotrebna je dalja diskusija o tome.

[ macolakg @ 26.08.2019. 11:35 ] @

I još nešto.

Pod "fail safe" se često podrazumeva neki oblik redudancije, odnosno sigurnosti nekog sklopa u primeni.

Zavisno od primene, to može biti jako šaroliko tumačeno.

Nekad se radi osiguranje od prekida kola, nekad od proboja, nekad od oboje...

[ Living Light @ 26.08.2019. 11:37 ] @

Branko u pravi si.

Njemu treba OC sa "PASIVAN IZLAZ", bez posebnog napajanja.

DSL,

Uzmi molim te, 4 komada posebna, svaki za sebe OC-a.

Jedan stavi na

-Zemlju,

Drugi na

-Mesec,

Treći na

-Mars,

I ćetvrti na

-Uran,

i poveži izlaze REDNO, kao što je na šemi,

i meri OSC-om vreme ukupnog kašnjenja.

[ DSL @ 26.08.2019. 11:38 ] @

Ja komedije...

Ovde jedino Macola kapira šta je problematika...

Da ste mi živi i zdravi svi odreda

[ DSL @ 26.08.2019. 11:40 ] @

Citat: Living Light:

Branko u pravi si.

Njemu treba OC sa "PASIVAN IZLAZ", bez posebnog napajanja.

DSL,

Uzmi molim te, 4 komada posebna, svaki za sebe OC-a.

Jedan stavi na

-Zemlju,

Drugi na

-Mesec,

Treći na

-Mars,

I ćetvrti na

-Uran,

i poveži izlaze REDNO, kao što je na šemi,

i meri OSC-om vreme ukupnog kašnjenja.

To je nešto sto sam uradio odmah, da si mi dobar...

[ Living Light @ 26.08.2019. 11:48 ] @

Citat: macolakg: Pod "fail safe" se često podrazumeva neki oblik redudancije, odnosno sigurnosti nekog sklopa u primeni.

Naravno.

U industriji je pravilo:

Alarmno stanje je uvek kada se nešto PREKINE!!!

Znaći:

Ne može ALARM da bude tako što tamo nečemu daš kontakt,

nego je alarm tada kada se prekine taj neki spoj/kontakt.

________________________________

Zašto se prešlo sa 0-20mA na 4-20mA ?

ZATO:

-Jer se 0mA ne zna da li je to 0% signala ili je neko odfikario kabl, na primer.

4mA je "ŽIVA NULA", ako nema ni tih 4mA, onda je ALARM.

Sistemi, koji "drže do sebe" proglašavaju ALARM već na 3.8 mA, ispod toga to se zove:

- OPEN CIRCUIT!

Ista situacija je i na 21mA, samo kontra  [ Living Light @ 26.08.2019. 12:04 ] @

Redudancija?

2 procesora, oba rade, usinhronizovano,

2 napajanja, oba rade i guraju struju u oba "svega",

2 memorije,

2 Maderborda,

2 x SVE !

Ako nešto, bilo šta rikne, ima ko da nastavi da "vozi postrijenje",

-ništa ne može da ide u vazduh  [ Living Light @ 26.08.2019. 12:06 ] @

Citat: DSL:

Ja komedije...

Ovde jedino Macola kapira šta je problematika...

Da ste mi živi i zdravi svi odreda

Jeste, ti to zbog prostora, jel?

Pa "zipuj" tu elektroniku malo više

Uzmi čekič i sabi to još više  ...da liči na japanski kanister, [ macolakg @ 26.08.2019. 12:12 ] @

Mogu se te stvari raditi i prostije a maksimalno efikasno.

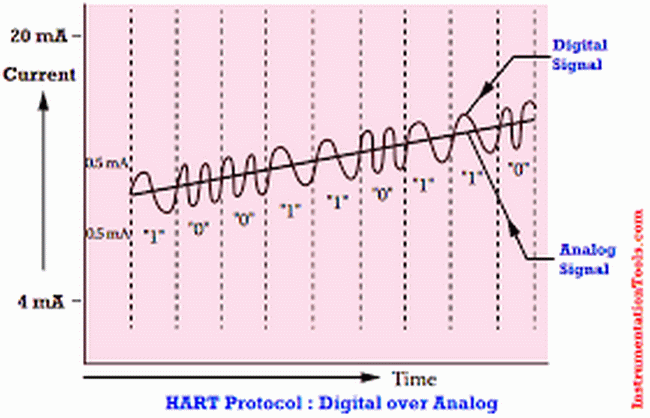

Kroz istu strujnu petlju se može voziti i pwm od +-1mA, gde se ne kvari srednja vrednost petlje od 4-20 a istovremeno ima još jedan AC signal za neke druge stvari...

[ Living Light @ 26.08.2019. 12:16 ] @

To se kaže: superponiranje DATA na LIVE signal = SMART sistemi

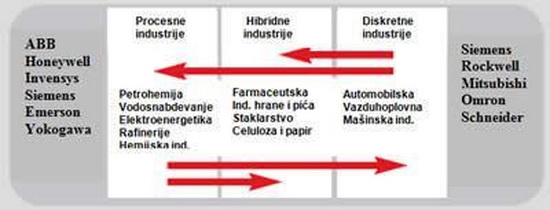

"Prednosti izbora „prave“ tehnologije automatizacije

U ovom dobu globalne konkurencije, proizvođači u procesnim industrijama prinuđeni su da postižu izvanredne radne karakteristike kako bi obezbedili mesto ispred konkurencije, sada i ubuduće. Izbor novih tehnologija automatizacije utiče na ovaj cilj. Kao posledica, da bi kompanija ostala jaka, proces izbora je važniji nego ikada ranije. U stvari, važnost izbora koncepta daleko je veća od značaja troškova same investicije u automatizaciju."

Izvor:

https://mehatronika.gomodesign.rs/dcs-ili-plc/

nego,

ajd da povežemo mi onih par elemenata, život će da prođe...

[Ovu poruku je menjao Living Light dana 26.08.2019. u 13:26 GMT+1][ scoolptor @ 26.08.2019. 12:22 ] @

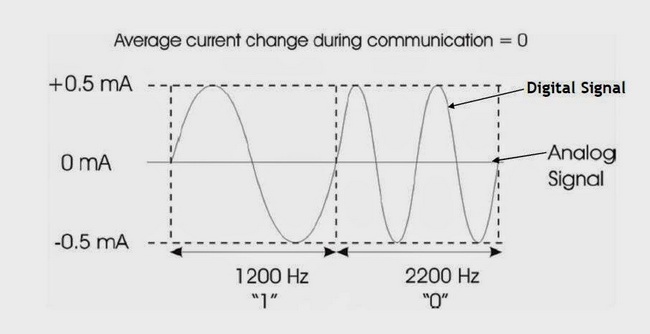

Tih 4mA se pretezno koriste za mogucnost napajanja senzora strujnom petljom.

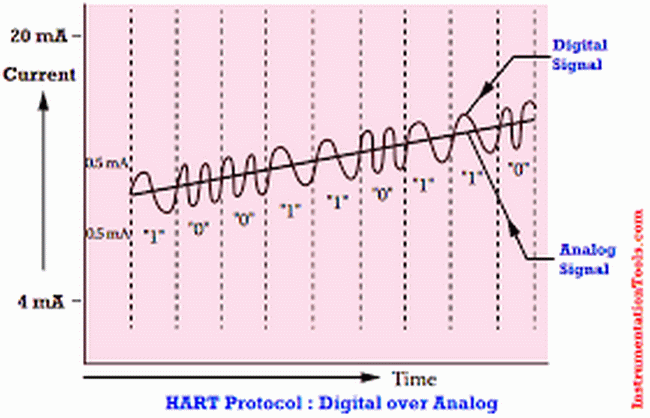

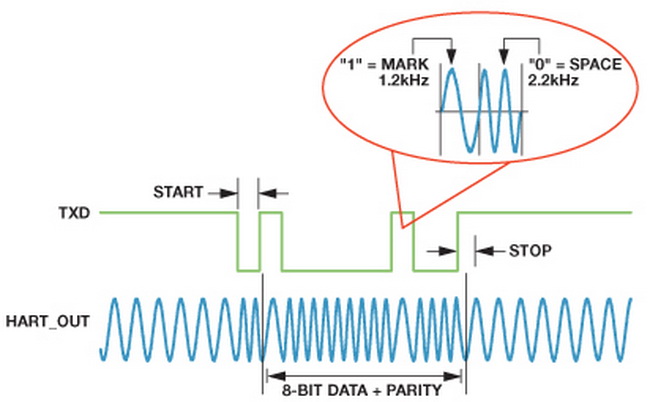

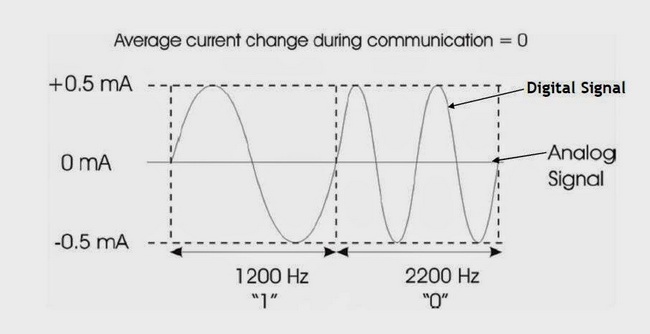

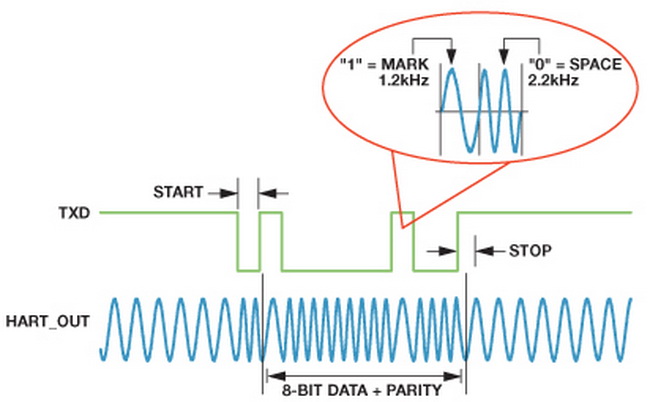

Sistemi koji podrzavaju HART superponiraju +-0.5mA sinusni signal razlicitih frekvencija za 0 i 1 na analogni signal strujne petlje.

[ macolakg @ 26.08.2019. 12:25 ] @

Robi,

Redudancija je čudo!

Neko izabere lošu zaptivnu gumicu i eksplodira šatl "Kolumbija".

Neko pre 56 godina zaboravi gumicu i sad ti pišeš po forumu :-)

Nemoj da mi se ljutiš Robi prijatelju. Morao sam da se malo našalim u tvom stilu.

Kako da izdržim kad mi je pala ta ideja na pamet :-)

[ Living Light @ 26.08.2019. 12:28 ] @

Hahahaha,

Ja stvarno ne znam, Tebe čime da uporedim?

Neuporediv  [ Living Light @ 26.08.2019. 12:34 ] @

Citat: scoolptor:

Tih 4mA se pretezno koriste za mogucnost napajanja senzora strujnom petljom.

Sistemi koji podrzavaju HART superponiraju +-0.5mA sinusni signal razlicitih frekvencija za 0 i 1 na analogni signal strujne petlje.

Tako je, povikoše seljaci :)

To o čemu doktor scoolptor piše, izgleda ovako:

To može i da se vidi:

https://www.youtube.com/watch?v=CK3R08RMDx0

[ branko tod @ 26.08.2019. 15:05 ] @

Citat: DSL:

Ja komedije...

Ovde jedino Macola kapira šta je problematika...

Da ste mi živi i zdravi svi odreda

Uvredio si me i kao čovek(a) i kao komunista(u) !!!!! [ Living Light @ 26.08.2019. 15:42 ] @

Čuti, dobro da DSL nije poželeo da budemo

-mtrvi i bolesni svi odreda :)

[ DSL @ 26.08.2019. 16:53 ] @

Ahah, ne znam samo koji deo je predstavljao uvredu...

Elem, ja pricah o sklopu u jednom kućištu, nigde ne pomenuh quad.

Kao sto ne pomenuh ni da je problem fail safe kao koncept nego samo realizacija AND logike sa optokaplerima...ali BRZA.

Elem, upravo sam dosao do resenja koje zadovoljava max delay kriterijum. Biranje i kontrolisanje struje kroz tranzistore u mnogome utice na brzinu celog kola.

Naravno, i izbor odgovarajućeg kaplera.

U prototip ce ici i dizajn koji je Macola ponudio kao alternativu.

[ Living Light @ 26.08.2019. 17:18 ] @

Citat: DSL: Kreiram neki bafer za vise signala ali koncept MORA BITI FAIL SAFE....

Imao sam ideju koja je podrazumevala da se katoda diode jednog vodi na kolektor drugog optokaplera ali to nije failsafe...

U prvom postu si rekao da mora, sada više ni to ne mora, kako?

Ebt, .nemci stigli do Kačareva, a mi se zezamo sa Fail-Safe, a mi stigli do Hart signala.

Nema veze DSL, i to če nekome trebati, ako ništa drugo.

Šta se promenilo u medjuvremenu?

[ DSL @ 26.08.2019. 18:53 ] @

U medjuvremenu sam, zahvaljujući savetima i dobrim dokumentima ponudjenim ovde, utegao ovo prvo rešenje sa latencijom manjom od 8us.

To rešenje ide kao prvi prototip ali će ići i drugo pa ćemo porediti rezultate...

Minimalizam u čitavoj priči je majka...

[ Living Light @ 30.08.2019. 03:58 ] @

DSL,

Javi bar kako si "utegao" to prvo rešenje?

Ne mora detaljno, znam da nemaš previše vremana,

čisto koju si šemu, i koji OC si koristio.

Znam da je trebalo na 5µs, sada je to 8µs,

ako to zadovoljava--dobro je!

Da li si uspeo da sabiješ na mali prostor?

Ako fercera -Drago mi je.

pOz

[ DSL @ 30.08.2019. 06:09 ] @

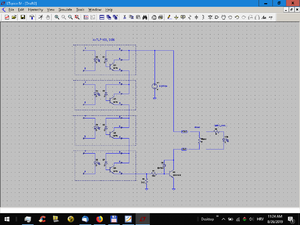

U stvari, latencija u citavom kolu je tvrdih 4us. Test stoji evo 3 dana, gledam da li ima neke promene sa vremenom ali je nema...

Stvar i jeste u tome da se otpori u kolu diode i narocito kolektora postave tako da se tranzistor ne odvede previse u zasicenje, nego da ga se drzi malo blizu ivice provodjenja. U praksi, iskoristen je koncept koji je Macola nacrtao (hvala jos jednom) a vrednost otpora u kolu emitera postavljena na 680R, prateci sve vreme na osciloskopu odnose krivih ulaznog signala, signala na LE diodi sledeceg stepena i napona na kolektoru izlaznog tranzistora...

Evo sad se vec zabavio sledecim problemom...

[ macolakg @ 30.08.2019. 14:44 ] @

Nema na čemu DSL.

Samo slušaš mene i ... zaglaviš u zatvoru :-)

Šalim se malo drugar.

[ Living Light @ 30.08.2019. 18:35 ] @

Dragoljube, Dragoljube,

"motka će da radi" ..samo Ti nas zahhebaj

Šalim se naravno,

Ee, sve što je macola na ovom forumu predložio, nacrtao,

-SVE RADI!

(Od čega li je taj čovek sastavljen?

mora da nije od "krvi & mesa")

-nego od nekih Ultra, Mega, Giga, Tera (iLi ne tera),

8k videa, (nit VIDEO nit čuo), procesori sa 24 jezgara,

UP-Down brat-bratu,

jedno tu negde oko ~ "LI-Fi" ....(naj novija tehnologija zastarelog WI-Fi -ja)

Brzina: samo pomisliš da nešto zamisliš

(zakasnio si) ONO već otišlo

-Jednom rečju strašno !

Čovek je STRAŠILO (ne za žene) nego za ELEKTRONIKU !!!

(ko mu dade prvu lemilicu, i prvi OSC)

.com [ macolakg @ 30.08.2019. 18:48 ] @

I drven šporet radi Roberte, ali samo jedan put :-)

[ Living Light @ 30.08.2019. 18:55 ] @

Xexex:

Tanjug javljaja: IZVOR hoće da ostane ANONIMAN

Ebt, kakva vremena su došla,

kada ja Tebi treba da kažem da se vratiš temi ?!

LJUDINO! _____B R A V O !!!

Copyright (C) 2001-2025 by www.elitesecurity.org. All rights reserved.

|